Please select your location and preferred language where available.

Kioxia Presented a False-lock-aware Locking Technique for 56-Gbps PAM4 Transceivers at ESSCIRC 2022

- October 4, 2022

- Kioxia Corporation

Tokyo- Kioxia Corporation, the world leader in memory solutions, announced the development of a false-lock-aware locking technique for 56-Gbps PAM4 transceivers at ESSCIRC 2022 (IEEE European Solid-State Circuits Conference 2022) on September 22.

Recently, one of the multilevel-modulation methods of PAM4 has started to be used instead of a conventional NRZ for network infrastructures which includes higher transmission speed and capacity such as data centers. However, when the PAM4 is used, a clock recovery can occasionally fail and then as a result the performance of receivers can be seriously degraded by the incorrect clock signals.

To address this technical challenge, Kioxia has developed the false-lock-aware locking technique to prevent the failure of the clock recovery. Kioxia will apply this false-lock-aware locking technique to high-bandwidth large-capacity memory modules for MEC (mobile edge computing) servers.

This development is based on a project commissioned by the New Energy and Industrial Technology Development Organization (NEDO).

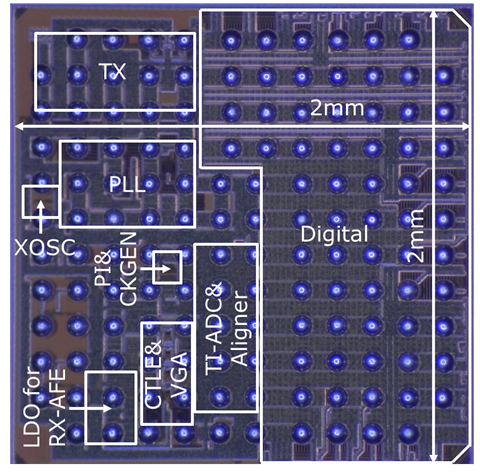

Figure 1 Chip micrograph of transceiver using 16nm-FinFET technology. ©2022 IEEE (*7)

1. Overview

Recently, demand for high-speed data communications has increased as a result of widespread adoption of 5G (5th generation mobile communication system), IoT and other technologies. In-network infrastructures such as data centers, one of the multilevel-modulation methods of PAM4 (*1), have started using these instead of a conventional NRZ (*2) for expanding transmission speed and capacity. The speed of a clock signal is twice that of a modulation rate (*3) of a data signal for conventional CDR (*4) circuits. However, a baud-rate CDR circuit whose clock speed is the same as modulation rate is now being used to reduce power consumption for the high-speed CDR. Unfortunately, a clock recovery occasionally fails and performance of receivers is seriously degraded by using the baud-rate CDR in PAM4 receivers.

To resolve this issue, NEDO and Kioxia jointly developed a technique for correct clock recovery. Firstly, comparators (*5) are operated in an NRZ mode to achieve the correct clock recovery, after which the comparators are updated to a PAM4 mode. A 56-Gbps PAM4 transceiver (*6) is fabricated using a 16-nm FinFET technology (Figure 1), and developed technique is verified by measurements of the fabricated transceiver.

Kioxia presented this development at IEEE European Solid-State Circuits Conference 2022 (ESSCIRC 2022), which was held in Milan, Italy on September 22 (*7).

2. Achievements

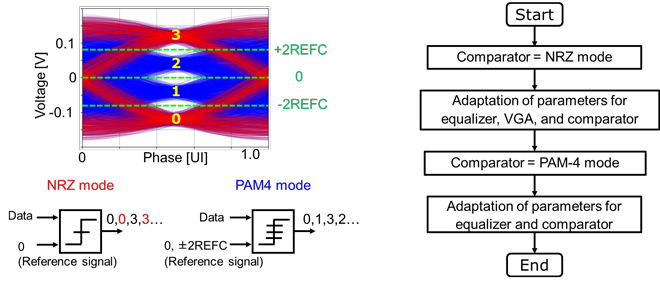

In the conventional baud-rate CDR circuits, the clock signal is occasionally locked at false-lock points as a result of misunderstanding specific transitions among data 0 and 3 as whole transitions of the PAM4 signal (Figure 2).

Figure 2 False-lock issue in baud-rate CDR circuits ©2022 IEEE (*7)

NEDO and Kioxia discovered that the clock signal is locked at the correct point when the comparators (*6) are operated in the NRZ mode even if the PAM4 signal is input. Therefore, the false–lock issue can be avoided by using the comparators in the NRZ mode. The comparators are first operated in the NRZ mode and then the parameters of the equalizers, variable-gain amplifiers, and comparators are adaptively controlled. Next, the clock signal is successfully recovered from the PAM4 input signal. After that, the comparators are changed to the PAM4 mode and the parameters of the equalizers and comparators are optimized again and the clock signal is adjusted properly (Figure 3).

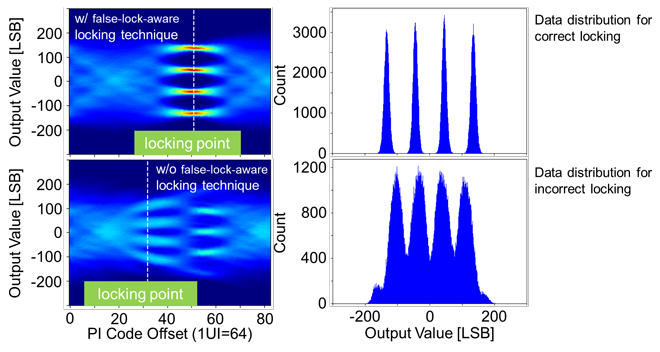

When measuring the fabricated receiver, 56-Gbps PAM4 signal is generated in the transmitter and then input into the receiver via an external cable. By using the proposed false-lock-aware locking technique, the PAM4 signal is correctly received even when the clock signal is locked at the false-lock point initially (Figure 4).

Figure 3 Proposed false-lock-aware locking technique

Figure 4 Measured results for false-lock-aware locking technique ©2022 IEEE (*7)

3. Future plans

Kioxia will be applying this false-lock-aware locking technique to a high-bandwidth large-capacity memory module using daisy-chain transceivers (*8). These are developing in NEDO’s project toward power consumption with less than 40 W, memory capacity over 5 TB and bandwidth over 64 GB/s.

By using such memory modules for big-data analysis in a 5G MEC servers (*9), digitization of industries such as IoT can be expected.

[Notes]

- PAM4 (4-level Pulse Amplitude Modulation)

Data transmission technique using four voltage levels representing two-bit data. Although one symbol contains one-bit data by using NRZ, one symbol transmits contains the two-bits data by using PAM4. - NRZ (Non Return to Zero)

Data transmission technique using two voltage levels representing “0“ and “1”. - Modulation rate

Number of symbol changes per one second, it is also called symbol rate or baud rate. - CDR (Clock and Data Recovery)

Technique recovering clock and data signals from received signals. - Comparator

A circuit which compares input-voltage and reference-voltage values. - 56-Gbps PAM4 transceiver

In this development, 56-Gbps transceivers for recent Ethernet technology of 400 GbE is assumed. - Title of the presentation

F. Tachibana et al., “A 56-Gb/s PAM4 Transceiver with False-Lock-Aware Locking Scheme for Mueller-Müller CDR,” IEEE

European Solid-state Circuits Conference 2022 (ESSCIRC 2022) - Daisy-chain transceivers

Multiple transceivers are connected between a memory controller and NAND flash memories using a daisy-chain configuration.

It is effective for high-bandwidth and large-capacity memory modules. - MEC server (Mobile Edge Computing Server)

Servers which are located near mobile terminals, it is effective to achieve low-latency communications.

- All company names, product names, and service names may be trademarks of their respective companies.

Information in this document, including product prices and specifications, content of services and contact information, is correct on the date of the announcement but is subject to change without prior notice.